MiZ702学习笔记12——封装一个普通的VGA IP

还记得《MiZ702学习笔记(番外篇)——纯PL VGA驱动》这篇文章中,用verilog写了一个VGA驱动。我们今天要介绍的就是将这个工程打包成一个普通的IP,目的是为后面的一篇文章做个铺垫。

打包成一个普通的IP的目的,可以直接将这个IP粘贴到Block文件中。(和用文本实例化是一个意思)。应为我们调用zynq的核的时候一般是用Block的形式,为了zynq和我们的VGA模块更方便的组织起来,就需要这种IP打包方式。

为什么是强调是普通的IP,这个主意是区分带AXI接口的IP,这个在后面介绍。

这个打包过程十分简单,新建一个vivado工程之后,准备好我们的VGA verilog源文件:

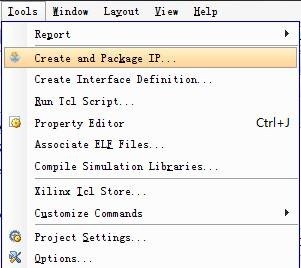

我将这些文件当中,当前工程下的song文件夹下备用。然后选择Tools Create and Package IP:

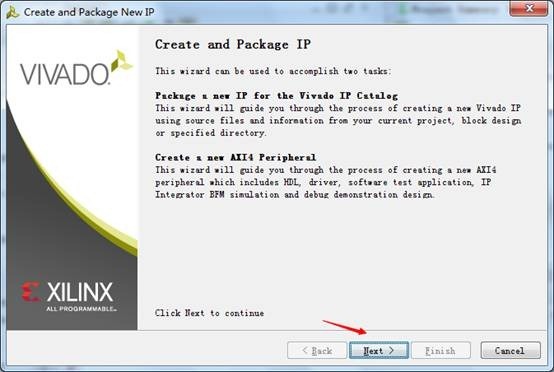

点击NEXT:

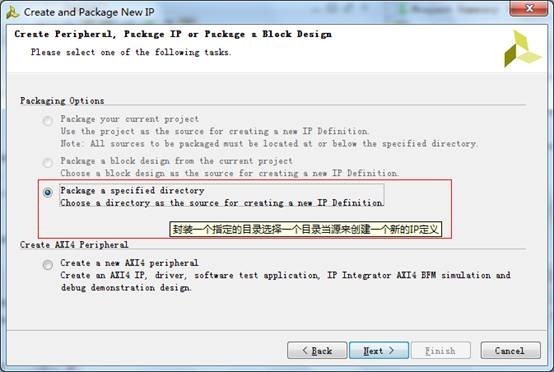

选择如下标记中形式的IP:

接下来是关键的一步,选择刚才我们准备好的源文件的位置,并点击NEXT:

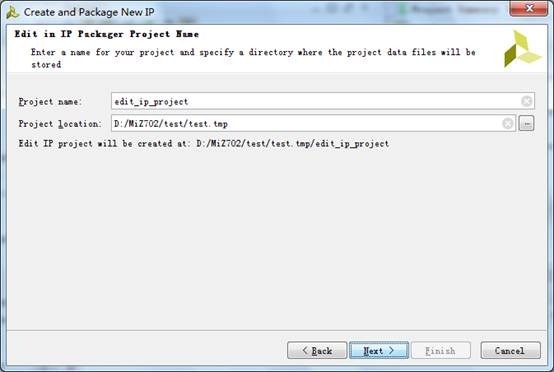

继续NEXT:

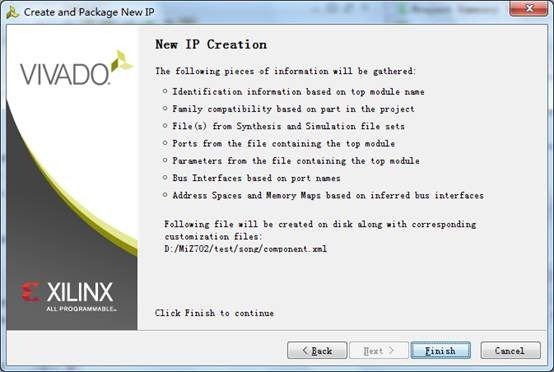

最后点击Finish:

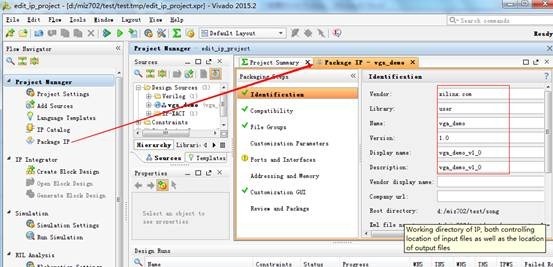

点击Finish之后,会自动创建一个新的工程,专门针对这个IP的工程。注意到红色方框内,有个name属性,这里他的名字就是你顶层文件的名字加上了一个版本号,软件自动给你填写的,记住这个名字,之后添加IP的时候,就是根据这个名字来找到我们的IP。

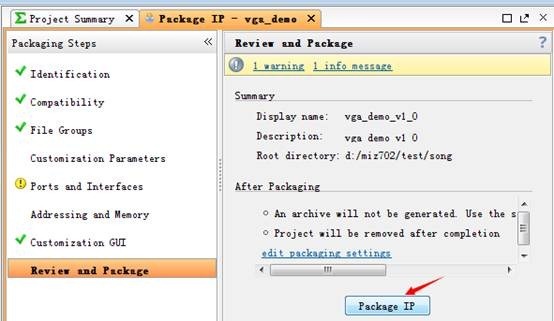

有个警告,懒得理他不影响,我们直接打包:

按下Package IP就完成打包了,这个工程就自动关闭了,回到我最先新建的工程,就可以添加我们打包的IP了。

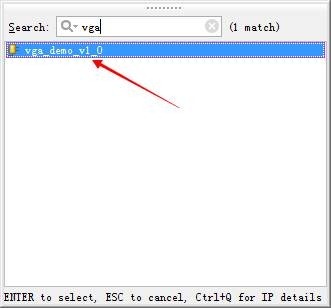

首先新建一个Block,然后选择add IP,搜索那个顶层文件的名字,就能找到啦~~

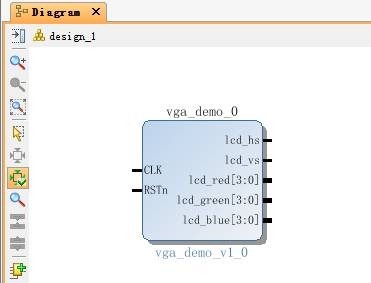

双击它,就可以添加到Block文件中了:

这种图形的实例化和文本的实例化,大家都需要熟练地运用,今天就到这里。

正文到此结束

热门推荐

相关文章

Loading...

![[HBLOG]公众号](https://www.liuhaihua.cn/img/qrcode_gzh.jpg)