关于硬件模拟的一点感知

设计一般以一个规范开始 , 这个规范能够约定最终产品应该做什么 , 并从根本上推动整个开发周期。在开发的早期阶段 , 第一个任务是使用规范来验证正在开发的设计是否正确无误的。然后当设计的所有部分组装成一个完整的系统时 , 第二个任务使用规范来确定系统是否也按照预期的方式运行。

这两个任务被称为设计验证 和验证设计 。有时 , 这两个术语可以互换使用。虽然相似 , 但这两个任务有着非常不同的目标。

· 设计 验证 : 我们建立的系统正确吗?

· 验证设计 : 我们建立了正确的系统吗?

在芯片系统设计过程中 , 采用基于软件的硬件描述语言 (HDL) 模拟方法进行设计验证。相反 , 验证设计是在实际使用的情况下对整个系统的原型进行验证。

不幸的是 , HDL 模拟执行速度并没有跟上设备的复杂性 , 尽管它有很多优点 : 易用性 , 灵活性和快速设计迭代时间。许多当前的设计 , 例如拥有 1024 个端口或高画质影像处理器的互联网路由器 , 需要大量的验证序列 , 即使在最快的 PC 上也需要很多年的时间来模拟。这些序列源自于需要运行长、连续的串行协议流 , 或者处理复杂的嵌入式软件来完全验证 SoC 或系统设计。

此外 , 在硅可用性之前开始软件验证已经变得非常重要。为了达到这个目的 , 可以 引入了一种叫做虚拟样机的新方法。虽然其中一些工具已经实现了启动软件开发的目标 , 但它们只涉及不需要精确表示硬件应用程序。当测试嵌入式软件 , 如固件、设备驱动程序、操作系统和诊断程序等嵌入式软件的交互作用时 , 它们就失败了。对于这个测试 , 嵌入式软件开发人员需要依靠一个精确的硬件模型来验证他们的代码。

相比之下 , 硬件设计师需要一套相当完整的软件来在系统验证期间完全测试它们的 SoC 。基于 FPGA 系统原型的方法提供了设计的精确表示 , 但不适合硬件调试。因此 , FPGA 原型对软件开发团队的吸引力更大 , 只要他们的设计适合一些 FPGA 。

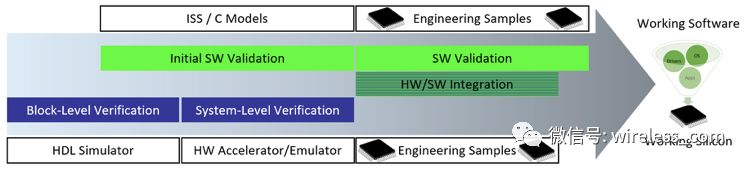

最终 , 软件和硬件组需要一起建立一个共同的模型来验证完整的硬件和嵌入式软件。对于大多数使用传统开发周期的 , 第一个完整的模型如 图 1所示 。

图 1 | 传统开发周期中的 第一个完整模型

因为嵌入式软件在一个完整的、精确的系统模型中无法被完全验证 , 所以在芯片中发现问题的可能性增加了。它们可以在软件或软件和硬件中找到 , 通常会迫使额外的芯片响应和代码的修改。逻辑和代码的修改都有成本和时间,对市场产生负面的影响。要避免这些影响 , 需要采取一种统一的解决方案 , 使硬件 / 软件验证及确认远远领先于第一个定制芯片。

最新一代的硬件仿真器实现了这一点。它们提供了几乎无限的容量 , 最多可以提供数十亿个门 , 并以1兆赫的速度验证正在测试的设计 (DUT) , 比 FPGA 原型系统提供了更好的硬件调试功能。它们很容易使用 , 可以更快地编译 DUT, 并且允许在 世界上任何地方 远程 访问。新的软件应用程序运行在模拟器上 , 使他们能够支持几种类型的验证 , 从低功耗分析和验证到测试逻辑验证的设计。模拟器还将独特的技术带到各种各样的市场领域 , 从网络到处理器 / 图形 , 存储等等。

在设计周期的早期 , 仿真器和 SystemVerilog 用于在组装完整的 SoC 设计之前验证IP块和子系统。在设计周期的后期 , 仿真器被用来验证整个系统 , 并执行嵌入式软件验证。

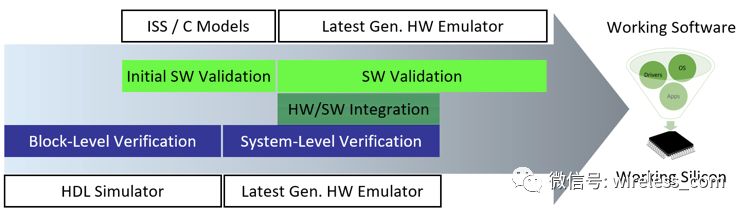

它们为硬件工程师和软件工程师提供完整的硬件和软件调试功能。这使得硬件和软件开发组合作并以一种以前不可能的方式解决集成问题 ( 图 2) 。

图 2 | 最新一代的硬件模拟器显著加速了开发周期

以前只限于对大型设计进行验证的硬件模拟 , 如今已成为所有设计验证及确认流的基础。这种新发现的流行是由于芯片定制复杂性的增加和嵌入式软件的广泛使用。在一个设计中心 , 在未来的整个开发周期中 , 从硬件验证、硬件 / 软件集成到嵌入式软件和系统验证 , 硬件模拟被使用 在整个开发周期中都可能得到广泛的使用。

(编译自 www.embeded-computing.com)

原文 https://blog.csdn.net/wireless_com/article/details/79911871

![[HBLOG]公众号](https://www.liuhaihua.cn/img/qrcode_gzh.jpg)