u-boot分析(四)---设置异常向量表|设置SVC模式

u-boot 分析(四)

通过前三篇的分析,我们对 u-boot 已经有了整体的认识和掌握,但是我们仍然对于其部分硬件是如何初始化的不太清楚,所以接下来几篇博文我将会对我们在 http://www.cnblogs.com/wrjvszq/archive/2015/01/10/4215627.html 一文中总结出的 u-boot 的工作流程中的重要环节,结合文档加以分析。

今天我们会用到的文档:

1. ARM Architecture Reference Manual : http://download.csdn.net/detail/wrjvszq/8354473

今天我们将会分析以下内容:

1. 设置中断向量表

2. 设置 CPU 为 SVC 模式

l 设置异常向量表

我们知道 arm 上电后 u-boot 干的第一件事就是设置异常向量表,那么什么是异常?异常又有什么类型呢?等等一大堆问题,下面我们一一解决。

1. 异常

异常其实是中断的一种,我们的中断按中断事件来源进行分类,主要有两类:

1) 中断: 由 CPU 以外的事件引起的中断,如 I/O 中断、时钟中断、控制台中断等。

2) 异常: 来自 CPU 的内部事件或程序执行中的事件引起的过程。如由于 CPU 本身故障、程序故障和请求系统服务的指令引起的中断等。

2. 异常的类型

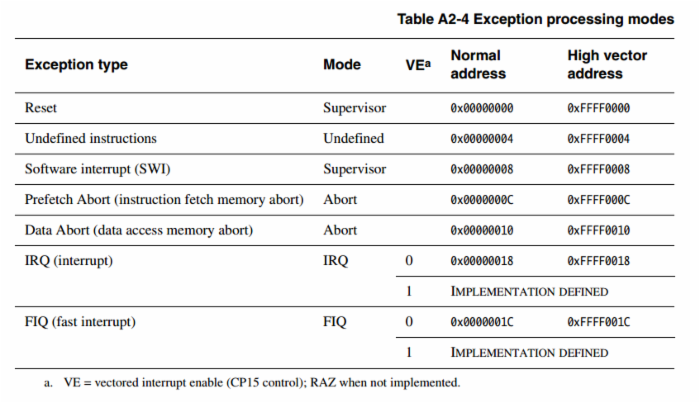

根据《 ARM Architecture Reference Manual 》手册中的 2.6 节我们找到了如下表格,说明我们的 arm 处理器支持的异常有七种

我们的 arm 处理器有两种入口地址,默认情况下我们选择 Normal address ,只有当设置了协处理器 CP15 的相关寄存器以后,才会启用 High vector address 。

特别提醒: Data Abort 和 IRQ 这两种异常的入口地址一个为 0x00000010 一个为 0x00000018 中间差了 4 个字节,在 arm 指令解析一节中我们提到 arm 的一条指令为 4 个字节刚好差了一条指令,所以我们看到 u-boot 这样设置异常向量表。

1 _start: 2 b reset //0x00000000复位异常 3 ldr pc, _undefined_instruction //0x00000004未定义指令异常 4 ldr pc, _software_interrupt //0x00000008软中断异常 5 ldr pc, _prefetch_abort //0x0000000c预取异常 6 ldr pc, _data_abort //0x00000010数据异常 7 ldr pc, _not_used//中间多差的一条指令。0x00000014 8 ldr pc, _irq //0x00000018外部中断异常 9 ldr pc, _fiq //0x0000001c快速中断异常

3. 异常向量:

当异常发生的时候,由硬件机制处理器 自动的 跳到一个固定地址去执行相关异常处理程序,而这个固定地址就是所谓的异常向量。

l 设置 CPU 为 SVC 模式

1. U-boot 工作的模式:

由于我们的 u-boot 需要执行更多的指令,访问更多的寄存器对芯片进行初始化设置,所以要工作在 SVC 模式。

注: 在 http://www.cnblogs.com/wrjvszq/p/4199682.html 一文介绍过 arm 处理器的工作模式

2. 如何设置 CPU 工作在 SVC 模式

同样在 http://www.cnblogs.com/wrjvszq/p/4199682.html 一文中我们介绍过通过 CPSR 寄存器设置处理器的工作模式,其实就是设置 CPSR 中的 M[0-4] 为 0b10011 这也就很容易明白 u-boot 为什么这么设置了。

1 reset: 2 /* 3 * set the cpu to SVC32 mode 4 */ 5 mrs r0, cpsr //导入CPSR寄存器的值到R0 6 bic r0, r0, #0x1f//0b1 1111对M[0-4]清零 7 orr r0, r0, #0xd3//0b1 0011对M[0-4]置1 8 msr cpsr,r0//将R0写入CPSR中

今天有点不舒服,所以就到此为止了,明天继续分析。

内容有点少,大家谅解!!!

![[HBLOG]公众号](https://www.liuhaihua.cn/img/qrcode_gzh.jpg)