张冬:OpenPOWER CAPI为什么这么快?

第七届中国云计算大会的PMC专场以“云计算与云存储核心架构与应用”为主题,当天下午七位演讲嘉宾轮番登场进行了七场演讲,其中,PMC数据中心存储架构师张冬没有过多谈论市场和行业问题,而是从底层技术出发对OpenPower CAPI进行了分析和阐述,为我们介绍了CAPI为什么能这么快!

PMC公司数据中心存储架构师 张冬

张冬,《大话存储》系列图书作者,PMC公司数据中心存储架构师。张冬先生是《大话存储》系列图书作者,该书屡次获奖,包括2008年十大IT畅销书排名第一,2009年全国技术品种畅销书。张冬在存储领域有多年的从业经验,主持并参与过多项创新存储技术的设计。

之前POWERCPU只是IBM在做小型机的时候使用,OpenPOWER开放后,成立了OpenPower基金会,基金会大部分成员都非常专注于CAPI(相干加速器处理器接口)上的利用,比如将外置的网络、GPU、闪存等设备通过CAPI直接与CPU相连接,并在此基础上根据不同的主流应用场景进行开放的、定制化的系统设计,PMC除了关注这些外还关注CAPI与NVMe进行协作的问题。

传统架构的缺点和瓶颈

现在无论是2路、4路、 8路还是32路服务器,他们架构中的CPU之间的互联有的是直联,有的通过NC(NC就类似以太网络里面的网桥)。核心之间要传输数据方式中,最高效的是共享内存,代码里写死。最低效的方法就是走网络,封装一堆的包出去,发送一个数据给远端的某个线程,调用一堆接口,走到协议栈,再到设备驱动,然后到网络,接着收包解析,这个过程非常慢。所以超级计算机没法做到CPU之间进行高速网络共享内存因为成本太高,没法将几万个CPU连接起来,只能走网络了,这也是松耦合系统的一个妥协。

没有CAPI的FPGA为什么也不太行

面对现在大数据分析、模式匹配、热点识别等,要求非常大的计算量,传统CPU出现瓶颈。普通的CPU其实也能计算,但是计算速度太慢,比如,只有64位宽来处理1GB数据,那便需要循环拆分N次才能算完,普通的CPU无法迅速处理这么大的运算量。

在多路CPU系统中,线程看到的都是单一的虚拟地址空间,这个虚拟地址空间会被操作系统映射到真实的物理空间里,但是所有的CPU看到都是同一份物理地址空间。

- 所有CPU看到单一物理地址空间;

- 所有Threads看到单一虚拟地址空间;

- PCIE物理地址空间映射到CPU物理地址空间;

- CPU物理地址空间也映射到PCIE物理地址空间。

有人想到硬件加速,做法就是把某个专业计算在电路层面展开,展开成更宽的位宽,更多的并行计算单元,去除一些不必要的缓存优化和流水线优化等,其实这就是专用运算芯片所做的,FPGA(Field-Programmable Gate Array,即现场可编程门阵列)是现场可编程的专用芯片上述就是所谓的硬加速。

在CAPI之前的FPGA怎么接入系统使用的呢?它是把FPGA做到一块PCIe卡里,FPGA通过CPU的PCIe控制器访问到主机内存空间。PCIe和CPU各自有各自的地址空间,CPU不能直接访问PCIe的地址,要先访问自己的地址,PCIE物理地址空间映射到CPU物理地址空间,反之CPU物理地址空间也需要映射到PCIE物理地址空间,这是个很费劲的过程。

数据出了ALU,面对复杂的路由网络,目的地址为内存地址,但是其相对外部网络的复杂性在于,目标的位置是不固定的,还可能有多份拷贝。 Need Coherency!硬件透明搞定Cache Coherency。CC不负责多线程并发访问cache line时的互斥,互斥需要程序显式发出lock,底层硬件会锁住总线访问周期。

如图所示是个四核CPU,每个CPU内部还有很多东西,每一个CPU的每个核心都有各自的缓存控制器,三级缓存控制器,每个CPU还包含内存控制器,PCIe控制器,QPI控制器(互联CPU相关),还有缓存一致性的控制器,他们全都接入一个高速的总线里面。多个线程看到的数据应该是时刻一致的,需要广播许多信息,这就是Cache Coherency,Cache Coherency Agent 负责把消息推送出去以及接受其他CPU发出的探寻。

多CPU之间广播量非常大,所以需要一个目录来记录本地的核心里面都有哪些缓存地址被缓存下来了。其他的CPU如果发广播来探寻,本地直接把目录查一下,如果没有命中缓存就直接不再往后端核心缓存控制器发消息,这样可以提升性能。所以说CC(Cache Coherency)很重要的,要确保线程看到同样的东西,同一个时刻,这叫实时一致性,且不允许异步。但是它不负责两个线程,如果互相都在写这份数据,会出现相互覆盖,这要靠(Cache Consistancy)软件解决。PCIe写内存也需要做CC(Cache Coherency),写入数据到某一地址,这个地址在其他的CPU缓存里,要把它作废掉。

在把FPGA做在一张PCIe卡上,PCIe卡总线接到CPU的情况下,PCIe要做哪些工作呢?

PCIe设备与CPU交互

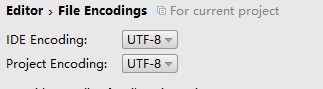

- Bus Driver将PCIE设备地址空间映射到CPU物理地址空间并将PCIE地址空间写入PCIE设备寄存器;

- Host Driver读出PCIE设备寄存器获取该设备对应的PCIE物理地址空间并ioremap()到内核虚拟地址空间;

- Host Driver 申请DMA缓存并向PCIE设备映射的虚拟地址空间写入控制字、基地址等,这些信息便被写入设备寄存器,从而触发PCIE设备根据基地址从主存DMA拿到需要的指令和数据后进行处理;

- PCIE设备对主存DMA时,RC自动执行Probe操作以保证Cache Coherency。

按照上面的过程走下来,缺点非常明显:

首先执行路径长而且全软件参与:应用call、传输协议栈、Host驱动、PCIe设备、DMA、中断服务、Host驱动、传输协议栈(如有)、应用buffer。

再就是PCIE设备和CPU看到不同的物理地址空间,RC进行映射和转换。驱动程序申请内存之后得用pci_map_single()映射成PCIE物理地址。虽然对于诸如Intel体系下,两个空间映射成一样的地址,但是仍需要在软件里做映射,这对性能有一定的影响。

另外,用户态程序必须主动从内核地址空间mmap()才可以直接与PCIE设备DMA互传数据。用户态程序必须区分不同的地址段,要分清哪一块内存是DMA映射的,哪一块是自己私有的的。

最后,FPGA上不能有Cache(缓存),FPGA自己可以有自己的Cache,但是不能把主存里的数据放在自己这边,每次访问内存都要用复杂的过程访问主存里,这也是一个关键的缺点。

所以我们看到为了让FPGA做一件事,进行了太多操作,开销很大,很费时间,这需要别的技术来解决之。

有了CAPI的FPGA是怎么做的?

首先认识一下这个体系里的三个角色:

AFU(Acceleration Function Unit) ,主加速逻辑部分就是FPAG的加速芯片,用户可以把自己的加速逻辑和Firmware写进去。

PSL(Power Service Layer), 提供接口给AFU用于读写主存和V2P地址翻译(与CPU侧使用同一个页表,并包含TLB),同时负责Probe CAPP实现全局cc,并提供Cache。PSL由IBM作为硬核IP提供给FPGA开发者。

CAPP(Coherent Attached Processor Proxy), 相当于FPGA侧的ccAgent,但是被放在了CPU侧,其维护一个filter目录并接受来自其他CPU的Probe,未过滤掉的Probe转发PSL。

操作要点可以简要的概括为以下6点:

- 针对专用场景、PCIE专用加速卡进行优化;

- FPGA直接访问当前进程的全部虚拟地址空间,无需转成PCIE地址;

- 加速卡上可以使用Cache并通过CAPP的Probe操作自动与主存cc;

- 加速卡与CPU看到同样的地址空间并且cc;

- 提供API,包括打开设备、传递任务描述信息等,相当于驱动程序;

- PSL由IBM提供,硬核IP。AFU通过opcode及地址控制PSL收发数据。

在这过程中,CAPI致力于把FPGA当成CPU的对等端,但这是一个特殊的CPU,对计算加速非常快的,非常高效的一个CPU。优势在于:两边看到了一样的地址空间,FPGA看到的不再是PCIe空间了,所以就省去了映射地址这一环节。再就是FPGA一侧可以有Cache,可以缓存主存里的数据,而且Cache是与主存一致的。

现在FPGA可直接访问主存空间,但它不会访问所有的物理空间,因为CAPI 1.0每个时刻只能给一个进程来用,CAPI会为进程会提供一个接口,打开FPGA之后发数据和指令。CAPI 2.0会让FPGA有一个分时复用机制,比如,每10毫秒跳一个线程,但是当前的FPGA不具备这个功能,只能是谁用谁打开。谁打开了FPGA就看到谁的虚拟空间。有了这种机制以后就不需要映射了,再就是可以直接访问内存地址了。还有Cache,基本就融入了所有的CPU了,就是一个对等、对称的关系。

性能能提高多少?

PMC做了许多测试,在测试过程中的硬件配置是这样的:

IBM Power8 Server, S822L

Ubuntu, kernel 3.18.0- 14-generic

Nallatech 385 CAPI card

Samsung SM1715 1.6TB NVM Express SSD

测试时,PMC工程师用FPGA制作了一个文本搜索引擎,如上图。

测试过程中,Host端主程序从NVMe SSD读入数据,并生成任务描述链表,AFU 采用pooling的方式访问主存获取任务描述链表并执行搜索任务,Snooper用来debug和性能监控。我们来看一下测试结果:

性能 – P8<->AFU

当队列深度60时的时候,获得一个极限吞吐量,接近6GB/s的带宽,带宽非常大。

延时也很小,只有1.5微秒,平均90%读写在1.5微秒完成。

CAPI 1.0暂时做不到的事情

现在CPU的线程看不到AFU上的地址空间(MMIO控制寄存器地址除外)。而且,AFU只能给一个进程使用。如果未来可以把FPGA直接接入CPU的FSB,是不是会更快?

更多精彩内容,敬请关注 第七届中国云计算大会直播报道 ,关注新浪微博直播 @CSDN云计算。

![[HBLOG]公众号](https://www.liuhaihua.cn/img/qrcode_gzh.jpg)